SynSense时识科技发布全新类脑感知及计算开发平台Speck及Xylo-Audio

SynSense时识科技宣布发布最新升级版Speck及全新Xylo-Audio类脑计算开发平台。此次发布的两款开发平台分别基于SynSense时识科技最新超低功耗“感算一体”的动态视觉智能SoC Speck及低维信号通用类脑处理器Xylo,同时提供配套开源软件(Samna、Sinabs、Rockpool、Tonic),主要面向高校及科研机构,支持教学、科学实验及算法研究,也可用于支持产业方进行超低功耗类脑视觉、音频等应用模型及算法开发。

SynSense时识科技全球研发副总裁Dylan Muir博士:“当前,已有海内外上百所顶尖高校和研究所,以及来自自动驾驶、智能便携、无人机/车、机器人等领域的行业客户使用SynSense时识科技的类脑开发板及工具链。我们旨在为开发者和爱好者提供更高效、更易于使用的开发工具,填补类脑相关开发平台的资源短板,助力前沿技术的交流应用与生态社区搭建。”

目前,Speck及Xylo-Audio开发套件已通过SynSense官方渠道限量发售。

欢迎咨询:联系我们 | SynSense 时识科技 (synsense-neuromorphic.com)

- 基于全球首款“感算一体”事件驱动的超低功耗AI视觉SoC-Speck(最新版)

- 升级动态视觉感知及计算,支持多场景超大规模类脑视觉感算一体应用开发

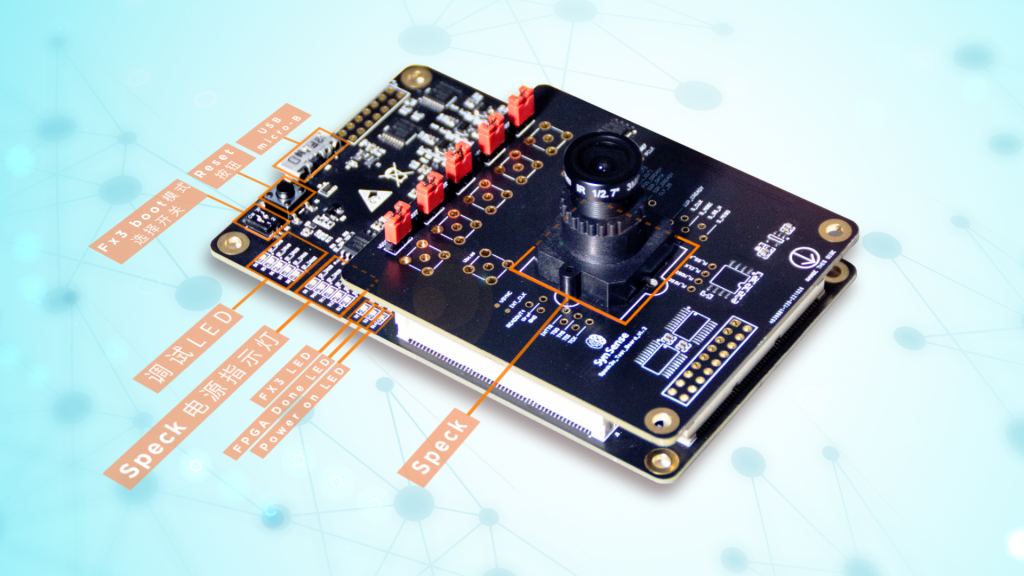

此次发售的Speck开发套件为SynSense时识科技最新款类脑视觉开发套件,全新升级的Speck SoC集成动态视觉传感器/事件相机,大幅度提升了感光性能并降低了噪声,同时,SoC片内集成32万脉冲神经元类脑智能处理器,实现超低功耗动态实时图像处理。利用SynSense时识科技开源软件开发包,可轻松使用片上DVS传感器并搭建高达9层的脉冲卷积神经网络。

Speck开发套件为SynSense时识科技目前在售的高性能类脑智能视觉开发平台,支持实时监测、手势识别、行为检测、光流、跟随等多场景复杂视觉类应用模型开发。

关键特征

搭载SynSense时识科技全新超低功耗“感算一体”的动态视觉智能SoC Speck

SoC芯片内置的DVS动态视觉传感器支持视觉分辨率128*128,并提升了动态范围

板载高精度功耗测量单元,用于实时监测SoC芯片各电源轨功率

板载SoC芯片各电源轨状态指示灯和系统复位按键

USB 3.0 Micro B接口

通过Samna实时查看DVS视频和监测SoC芯片输出(读出引脚)

Speck类脑视觉开发套件交付内容:Speck开发板(子母板)、2只镜头(3.6mm/1.7mm)、USB3.0线缆、Get Started说明卡。开源库Sinabs、工具链Samna及相关指导服务。

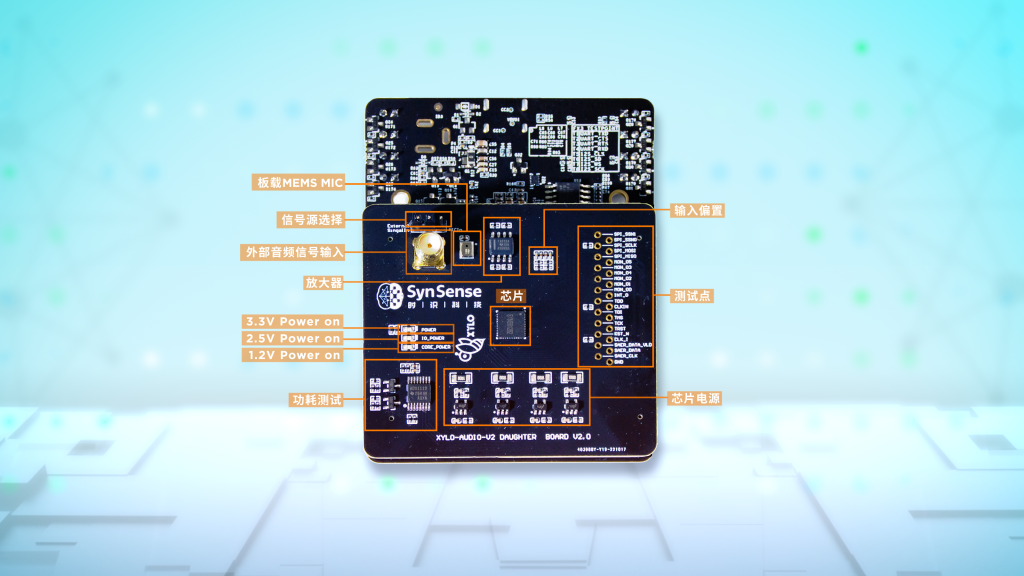

- 为首次发布的超低功耗低维信号通用类脑处理器开发套件,搭载SynSense时识科技基于脉冲神经网络的低维信号类脑处理器Xylo-Audio

- 微瓦级功耗音频处理,高度实时的音频处理性能。

全球首次发布的Xylo-Audio开发套件适用于微瓦级功耗的音频AI任务,具备高度实时的音频处理性能,擅长关键词识别、场景检测、事件音判断、声纹识别等复杂音频AI场景;且芯片内置LDO可进一步降低系统BOM成本。Xylo-Audio开发板搭载高性能MEMS麦克风、板载高精度实时功耗测量单元,能够高效地对音频特征进行处理,并预留了外部低维度信号输入接口,支持压力、震动、加速度等其他类型传感器智能应用开发。

SynSense时识科技同时提供开源软件开发包安装脚本和演示,只需几行命令,即可完成软件安装和示例算法模型部署。

关键特征

搭载SynSense时识科技的低维信号类脑处理器Xylo-Audio

板载高性能MEMS麦克风

板载高精度功耗测量单元,用于实时检测芯片各电源轨功率

支持切换芯片内部电源输入、片上LDO

预留SMA接口,用于外部输入低维度信号

USB3.0 Type-C接口

集成脚本,支持自动化快速安装软件

Xylo-Audio低维度音频信号类脑开发套件交付内容:Xylo-Audio开发板(子母板)、USB3.0线缆、Get Started说明卡。Rockpool和Samna工具链及相关安装指导。

加入SynSense时识科技

类脑智能开发者生态

类脑智能正在逐渐走进大众视野,在科研和技术领域,开发者和爱好者正在密切关注类脑智能或已在其中展开探索,却面临开发工具、开发条件不完善的挑战,对研发工作的展开形成一定限制,也致使类脑技术的更广泛推广壁垒重重。对于类脑计算和应用落地,甚至脑科学研究,开发套件和工具链的完整性至关重要。

自成立以来,SynSense时识科技密切关注来自高校、科研机构及行业的需求。以核心团队在类脑技术领域的强大实力为基础,SynSense时识科技先后发布了一系列开发板及开源性质的多用途工具链,实时提供全新的类脑开发平台并丰富开发资源,助力开发者更快速地进行脉冲神经网络模拟、训练、部署以及相关应用的测试开发。

“SynSense时识科技首发类脑开发板及配套工具链,在降低类脑技术触及门槛的同时,旨在完善开发者学习、交流及应用的基础环境,我们期更多开发者和爱好者加入类脑领域,共同助推类脑智能取得新的突破,” 乔宁博士表示。

Muir博士表示:“SynSense时识科技成立前,在类脑脉冲神经网络硬件上设计、建立及部署应用需博士级专业知识和3-4年左右的时间。而如今当一位实习生加入SynSense时识科技,在1-2个月之后便进行了首次脉冲神经网络应用部署。这是一项巨大的进步,有利于类脑智能开发者生态的搭建,也是对SynSense时识科技类脑工作的巨大回报。”